Project and grants for S&YP

Student Challenge - Challenge for secure and trusted learning standards

This annual Student Challenge is supported by the IEEE Standards Association (IEEE SA), Industrial Electronics Society (IES) and Computer Society (CS) that give students the opportunity to apply their knowledge in Artificial Intelligence, Programming, and web design for trusted and secure platforms, webs and applications.

Areas of development:

- Web browser Forensic tool to monitor events in application.

- Virtual Router.

- Secure repository of educational content.

- Validation of identity of student in a Synchronous Online Educational session.

- Classroom secure gadgets for the classroom (smartboard, clickers).

- AR and VR tools to facilitate visualization of Concepts.

- etc

1st prize – 3000$

2nd prize – 2000$

3rd prize – 1000$

The deadline for registration is 25 of September and the final competition will be done in Spain, Universitat Politecnica de Valencia during 14 and 15 November.

For more information please click the following link:

_____________________________________________

HILRES'22 Summer School: Hardware in the Loop for Renewable systems with SoC platforms

Royal Holloway, University of London is organizing the first Summer School for young researchers, technically sponsored by ESoC Technical Committee of IES IEEE.

The event provides Master and PhD students, lecturer, researchers and engineers from academia and industry the opportunity to design/implement and hardware/software co-simulate a renewable energy system.

HILRES’22 aims to providing a three-day design from scratch experience of a bare-metal SoPC based Hardware in the Loop platform to model, simulate and control a complete Photovoltaic (PV) system using various design methodologies on low-cost SoC platforms.

HILRES'22 key activities:

- Fundamentals of a photovoltaic system.

- Controlling a photovoltaic system.

- Matlab/Simulink modelling and simulation of a photovoltaic system

- SoC & Zynq Architecture (heterogeneous SoC, Processor System, FPGA, architecture and interfacing)

- Designing with the Zynq (hardware design definition in Vivado using IP Integrator, custom IP, software development using Vitis and Petalinux).

- Core to Core Communication (synchronous and asynchronous communications, interface definition and selection, internal communication between different processor cores).

- SoC FPGA Hardware/software co-design of a photovoltaic system with PYNQ boards (Dual-core ARM Cortex-A9 processor, I/O, Timers, interrupts

- VHDL fundamentals

- Co-simulation and FPGA in the Loop simulation of a MEPT controller.

- FPGA-based for Ac drive applications

- Hardware in the loop fundamentals

- SoC FPGA Hardware/software co-design of a photovoltaic system with PYNQ boards (D/A and A/D converters, PWM), Power converters on-chip modelling.

Keynote speakers, lectures:

- Prof Mickael Hilairet, University of Bourgogne Franche-Comté, FR, (PV system modelling and control)

- Prof. Adam Taylor, Adiuvo Engineering and Training Ltd, UK (SoC design)

- Prof. Tarek Ould-Bachir, Polytechnique Montréal, CA (Power converters on-chip modelling)

- Dr Lahoucine Id-khajine, Cergy-Pontoise University, FR, (FPGA acceleration, Design tools)

- Dr Alin Tisan, Royal Holloway University of London, UK (SoC, VHDL design)

Registration fee (£300) includes:

- Access to the Summer School tutorials and Lab activities

- 3-day Full Board (accommodation and all meals included) at Royal Holloway, University of London Campus

- Coffee breaks, refreshments

- Gala dinner

For more information please click the following link:

_____________________________________________

Research and Training Network for Smart and Green Energy Systems and Business Models

Project Number: 955614

Project's acronym: SMARTGYsum

Financial Program Name: HORIZON 2020

Organization: European Commission

Start: 2021-10-01

End: 2025-09-30

Project description

Figure 1. Geographical coverage

Figure 2. Training structure of SMARTGYsum project

Project organization

The proposed ETN SMARTGYsum is organised in 7 Work Packages (WPs),corresponding to the stated objectives, following an internal structure depicted in Figure 3. The achieve the stated research objectives, SMARTGYsum will use a research methodology that combines engineering and business models, based on the design and computer simulation, using advanced techniques of digital twins, development using laboratories prototypes or preliminary versions of software appliances, including rapid prototyping and hardware in the loop, experimental validation in given scenarios, as closed as possible to real cases, and finally the definition and test of business models using simulation and small application cases, when possible during the secondments at non-academic sectors. This will enable the coupling of the technological requirements with the related changes needed in the socioeconomical context.

Figure 3. WP structure for implementing the SMARTGYsum project

Gdańsk University of Technology will participate in WP3: Smart energy distribution, microgrids and grid of microgrids: which is aimed to explore the possibilities of microgrids for energy management to address the challenges of secure energy routing and power quality control, as well as advanced distribution grid management and the use of radial grids. WP3 is focused on development of EV chargers and active bidirectional charger able to provide ancillary services. Development of new power electronics facilities for energy transfer system with improved efficiency and power density as well as an analysis of future energy system including wireless charge system for electric vehicles are the main WP3 objectives. As a final result a prototype of bidirectional energy charger for providing ancillary services and development of strategies for optimized electric grid management are expected.

For more information please click the following links:

https://smartgysum.eu/

https://cordis.europa.eu/project/id/955614/pl

https://mostwiedzy.pl/en/project/systemy-smart-green-energy-i-modele-biznesowe,848-1

Recruitment for WP3 realized at Gdańsk University of Technology

Gdańsk Tech invite applicants for a PhD Fellowship in Green Energy Systems to research in the topic titled “EV chargers, developing an active bidirectional charger able to provide ancillary services.”

The position is in the frame of a H2020 Marie Skłodowska-Curie Innovative Training Networks (ITN) action for Early Stage Researchers within the project SMARTGYsum (Research and Training Network for Smart and Green Energy Systems and Business Models). The grant covers up to 3 years (contract will be for 1 year with renewing possibility) of full time research according to salary table established in the grant for Poland. Deadline for application submission is 2021-11-30 24:00 (CET), UTC +1 and starting day is planned on 2022-03-01.

SMARTGYsum (SMART Green energY Systems and bUsiness Models) project groups together leading European Universities and Institutions (the consortium is composed by 13 universities and 14 companies/institutions) with the aim to implement a multidisciplinary and innovative research and training programme, bringing to enable a new generation of Early Stage Researchers (ESR) to foster a New Green Energy Economy in Europe. ESR will acquire the knowledge, methods and skills across a wide range of disciplines around the Energy ecosystem, Renewable Electric Energy Systems and Business Models for the deployment of the Green Energy System. Trained ESR will have the technical and economical knowledge to break the barriers for the deployment of energy transition as market and social barriers (price distortion through externalities, low priority of energy issues, split incentives); financial barriers (investment, high up-front costs, lack of access to capital); information failures (lack of awareness, knowledge and competence); or regulatory barriers (restrictive procurement rules).

For more information please click the following link:

Student and Young Professionals Resources

2021 IEEE-IES Student and Young Professional Competition Presentations

Click here to watch all uploaded videos.

Useful links:

IEEE Industrial Electronics Society Youtube channel: https://www.youtube.com/channel/UCKg8GNii0Q-ieXE56AXosGg

IEEE Industrial Electronics Society Facebook profile: https://www.facebook.com/pg/IndustrialElectronicsSociety/events

IEEE Collabratec®: https://ieee-collabratec.ieee.org/app/community/129/Industrial-Electronics-Students-and-Young-Professionals/activities

LinkedIn group :https://www.linkedin.com/groups/3124640/

Updates

The most recent updates in The IEEE IES Student and Young Professionals Activity Committee (IEEE IES S&YPs-AC) live can be found in the files :

Important note IES Student Paper Travel Awards (IES SPTA) changed its name to IES Student Paper Travel Assistance - all conditions remain the same.

Since last IECON'15 in Yokohama IES Student Paper Travel Assistance (IES SPTA) are distributing between Students in our Society. In March 2016 at ICIT first time 6 awarded students: Yuchen Jiang, Harbin Institute of Technology, China for paper entitled "Study on recent developments of residual generation design approach based on available process measurements; Apparao Dekka, Ryerson University, Canada, for paper entitled: "Dual-Stage Model Predictive Control of Modular Multilevel Converter"; Shambhu Sau, Indian Institute of Technology, Bombay, India, for paper entitled "High-Power Regenerative Cascaded Multicell Converter with Multilevel Input and Output"; Jinya Su, Loughborough University, United Kingdom, for paper entitled "Fault Diagnosis for Vehicle Lateral Dynamics with Robust Threshold"; Hyuntae Choi, The University of New South Wales, Australia, for paper entitled "Hybrid Energy Storage for Large PV Systems using Bidirectional High-Gain Converters"; and last but not least Umesh B S, Indian Institute of Technology, Hyderabad, India, for paper entitled "Generation of Multilevel Voltage Profile for Torque Ripple Reduction of a 15 Phase Pole-Phase Modulated Induction Motor Drive Using Two-level Inverter Structure" prepared and presented three minute speech (3Ms) with movie in background to present their project during the conference and in IES Facebook page under ICIT2016 event the link is placed in reference.

In this year we are going to support by IES SPTA also another conferences namely: ISIE, INDIN, ETFA, CPE-POWERENG, IECON and PEMC (as a memorial of prof. Istvan Nagy)

Introduction to the IEEE IES Students and Young Professionals Activity Committee (SYP-AC)

The IEEE IES Young Professionals & Student Activity Committee (YPS-AC) refers to a team of volunteers devoted to support the most active Young Professionals & Student all over the world. We are doing our best to attract new members to the IEEE Industrial Electronics Society (IES).

The YPS-AC supports selected IEEE IES conference publications authored or co-authored by the IEEE IES Students and/or Young Professionals (YPS) through the travel cost reimbursement up to US$2000. In co-operation with the main IEEE IES conferences as IEEE International Symposium on Industrial Electronics (ISIE) and IEEE Annual Conference of the IEEE Industrial Electronics Society (IECON) or the IEEE International Conference on Industrial Technology (ICIT), this committee organizes scientific forums, tutorials, industry links and social events especially for YPS.

Finally, YPS-AC selects and promotes the best student presentations during the forum by prestige recognition of up to US$750.

Please read the following information to learn more details about the above-mentioned activities and benefits.

In order to clarify who is a Young Professionals & Student (YPS) member, let us explain this briefly. In the IEEE we have the membership ranks of Student and Graduate Student. "Student member must carry at least 50% of a normal full-time academic program as a registered undergraduate or graduate student in a regular course of study in the IEEE designated fields. The total cumulative period for a member to hold the Student member grade and/or the Graduate Student member grade is limited to eight years" [1].

Do not worry if you have completed your study and received your first professional degree. In this case, you can become a Young Professional (YP) IEEE member automatically, for up to 15 years after your graduation. Moreover, the help of more experienced professionals is needed to network with and mentor Young Professionals [2]. Therefore, the IES members are all ‘young at heart’ and cooperate.

The IEEE IES is going to form a platform for Mentors and Mentees to cooperate not only in the laboratories of the Academia but also interact at the scientific conferences.

Industrial Electronics Society  at YouTube

at YouTube  powered by Student & Young Professionals Activity Committee (SYP-AC)

powered by Student & Young Professionals Activity Committee (SYP-AC)

Please visit link: https://www.youtube.com/channel/UCKg8GNii0Q-ieXE56AXosGg/featured

Attraction and benefits for SYP-AC

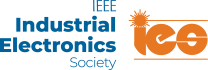

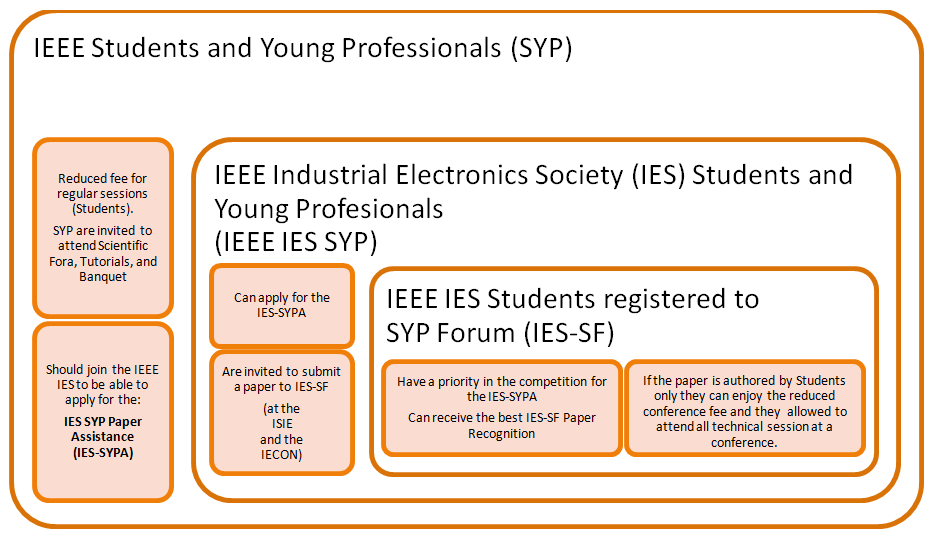

The YPS-AC is continuously working on various offers for young scientists by introducing/organizing travel reimbursements, paper recognitions, scientific fora and social events (Fig. 1). The main activities are described below.

Fig. 1 A special benefits for IEEE Industrial Electronics Society (IES) Young Professionals & Student (YPS) - block diagram.

Guidelines for Students and Young Professionals

Instruction regarding the travel reimbursement procedure for awards

A generic instruction regarding the travel reimbursement procedure for awards is available here.

Presentation Guidance

The IES-SF offers you a great opportunity for showing to the IES community your work and results. However, you should take into account some suggestions when you prepare your presentations in order to be successful with this task and become a potential candidate for an award. Guidance follows:

ORAL PRESENTATIONS

-

Avoid using more than 6 lines of text and minimize the number of words on each visual effect.

-

Plots should have a maximum of three data traces.

-

A fast presentation is one slide per minute. A more relaxed pace would be two minutes per slide. Adjust the number of slides (12 to 15 main slides max). Remember you have only 15 minutes for the presentation and five minutes to answer all questions.

-

Simple is better, avoid a lot of unnecessary formatting. We are interested in your technical content, not your PowerPoint skills.

-

Put your company or university logo on your title slide only; this is a technical presentation to your peers, not a marketing pitch to a customer.

-

Computer presentation works well when using dark background with light text and color scheme. Avoid flashy Christmas light multiple colors and other distracting means.

POSTER PRESENTATIONS

-

In the Young Engineers’ Poster Session, young engineers will have the opportunity to show their works to experienced engineers and companies in a friendly way.

-

Authors are expected to set up their Posters before the start of the poster session. More details will be given in the final program of the conference.

-

Poster presentations are a different style of conference activity; you are advised to take the time to prepare your material well. Please note that you cannot just pin up copies of your published paper since it is not allowed.

-

A good poster display will catch the eye of the viewer, present logical sequence of material in a visually appealing way, and not require the reader to examine large tracts of detailed text.

-

The concept of the young engineers’ poster session is that students remain at or near their paper, and engage in direct discussion with experienced engineers as they come by. This type of presentation allows for more in depth discussion with the audience, and provides the opportunity for extended interaction where there is a mutual interest. However, it only works if Authors are available for discussion so please don’t just hang your poster and walk away. Keep these ideas in mind when preparing your poster.

THREE MINUTES SPEECH (3Ms)+MOVIE

Your 3Ms speech should be clear and attractive. You have to prepare also a movie and place link to the movie on YouTube and IEEE IES Facebook. During the conference you will present live your 3Ms with the movie in background. The movie has to be accessible by the Internet so remember to mention some following points when you are preparing this form of your project presentation:

-

At the begging Author should introduce himself and his University and IEEE IES (please use university and IEEE IES logos) give the title of your paper and authors list - add two or three sentences, it could be as subtitles.

-

Then the video should present Authors laboratory setup (if not applicable please present the main theory basic and how the methodology was selected and software, etc.), simulation model, wave-forms, and something related directly with your subject, what is exciting in your research.

-

According to voice: please consider that some voice from your test bench, applications would also be interesting - if exists. You can add some music or just narration with subtitles.

-

Remember that your speech during the conference (probably just before the IES-SYPA diplomas ceremony) will be live with background of your movie (all details according to when and where will be provided by Chairs of the conference).

-

The video should be available on YouTube, and Research Gate before and after the conference. The deadline will be provided after IES-SYPA competition results announcement.

-

Please remember that the most important thing is: show hardware photos, movies if you have also hardware solution. Operating laboratory setup showing some action (movement, lighting etc.) should be shown in the video.

-

Show the design process such as designing the electronics board, soldering the parts, wiring. If you do not have a hardware please do this with your software tools how your model looks like, waveforms, animations etc.

-

Put some examples showing applications and impact of your work on the market, science etc.

-

Your video clip should look like an attractive announcement of new product on YouTube, for example; just search some to get the idea how to advertise in an appealing way.

-

At the end, you would include thanks to IEEE IES and S&YPs-AC - give the links to your website, IES Facebook, LinkedIn, IES Student website, your University website, acknowledgment, etc.

-

Please respect copyrights of another authors.

All recipients of IES-SYPA have to prepare 3Ms+ movie and declare its availability during the conference.

SYP-AC’s people and roles

The Students and Young Professionals Activity Committee (SYP-AC) currently consists of:

-

Chair of the IEEE IES Student and Young Professionals Activity Committee (YPS-AC):

Dmitri Vinnikov (dmitri.vinnikov@taltech.ee);

-

Co-Chair of the three minutes’ speeches (3Ms)+movies, e-promotion and exhibition:

Hani Vahedi (hani.vahedi@ieee.org);

-

Co-Chair of the Student Forum and Industry Link:

Andrii Chub (andrii.chub@taltech.ee);

- Co-Chairs of the YPS Members activities, Cooperation with Web and Information Committee::

Marek Turzynski (marek.turzynski@pg.edu.pl);Edivan Laercio Carvalho da Silva (edivan.carvalho@taltech.ee);

- Past Senior Chairs of the YPS-AC:

Moreover, the YPS-AC can successfully manage all the activities mentioned above thanks to the valuable support from IES President, VP for Membership, IES Treasurer, IES conferences Chairs and all IES volunteers which stimulate and support our activity.

Summarizing all of the above - please consider becoming the IEEE IES student or young professional member and help us to promote new knowledge and interact proactively in our welcoming professional environment. We are looking for new volunteers!!!

"In you there is hope, for you belong to the future, just as the future belongs to you. For hope is always linked to the future; it is the expectation of ‘future good things’" [8].

References

- http://www.ieee.org/membership_services/membership/join/index.html

- https://www.linkedin.com/company/ieee-young-professionals

- https://www.facebook.com/events/1835441829929519/

- http://www.ieee-ies.org/members/treasurer-information

- http://www.ieee.org/societies_communities/geo_activities/forms_petitions/forms_petitions_index.html

- http://www.ieee-ies.org/students/reports

- http://www.ieee-ies.org/members/wic

- prof. Karol Wojtyla